From indiegogo campaign begin, I received a lot of emails, some people said they are very excited and can not wait for it, some people send us special thanks for making it. But also I find some people emailed me, they want it so bad but just can not afford it yet.

My target for VoCore is to dig electric physics limit and my skill limit, make it to the best and do it to the extreme, it is a test for myself so I do not care much about its cost, but their request light my brain again, is it possible to make a wonderful thing but it also can be afford by the budget limited people such as students?

RaspberryPi zero is very good, only 5USD, its price is low and everybody can afford it. I waited the exciting thing over six months, try to get one but never success, it is too hard to buy 🙁 sometimes I just think it is not that real :p

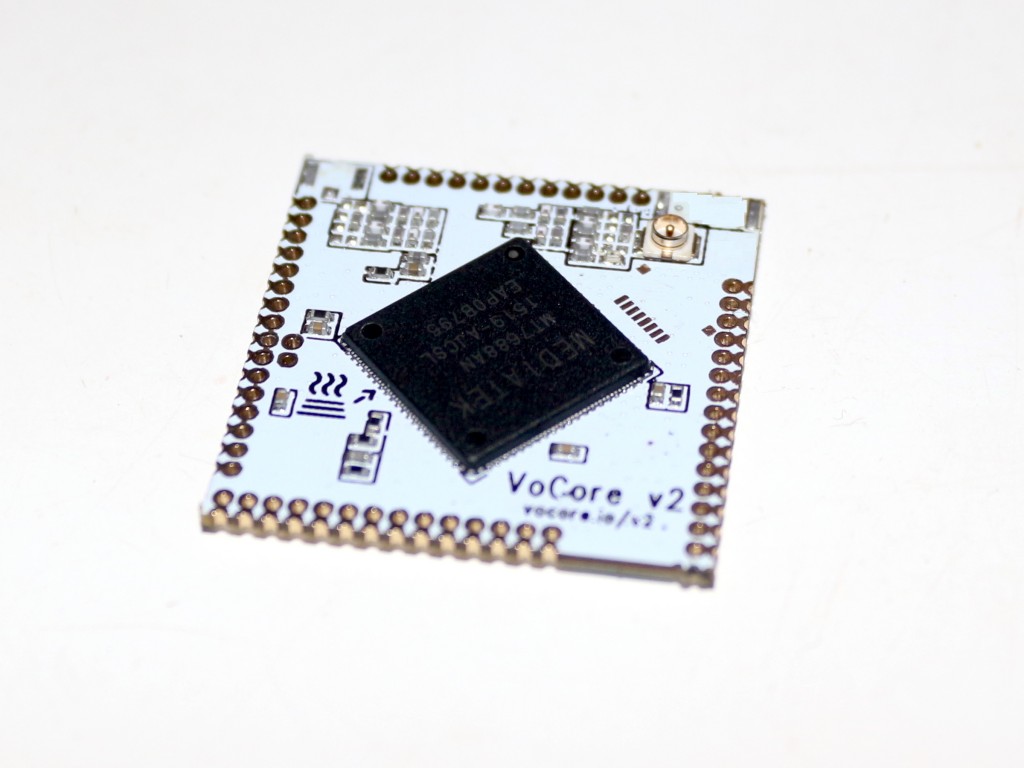

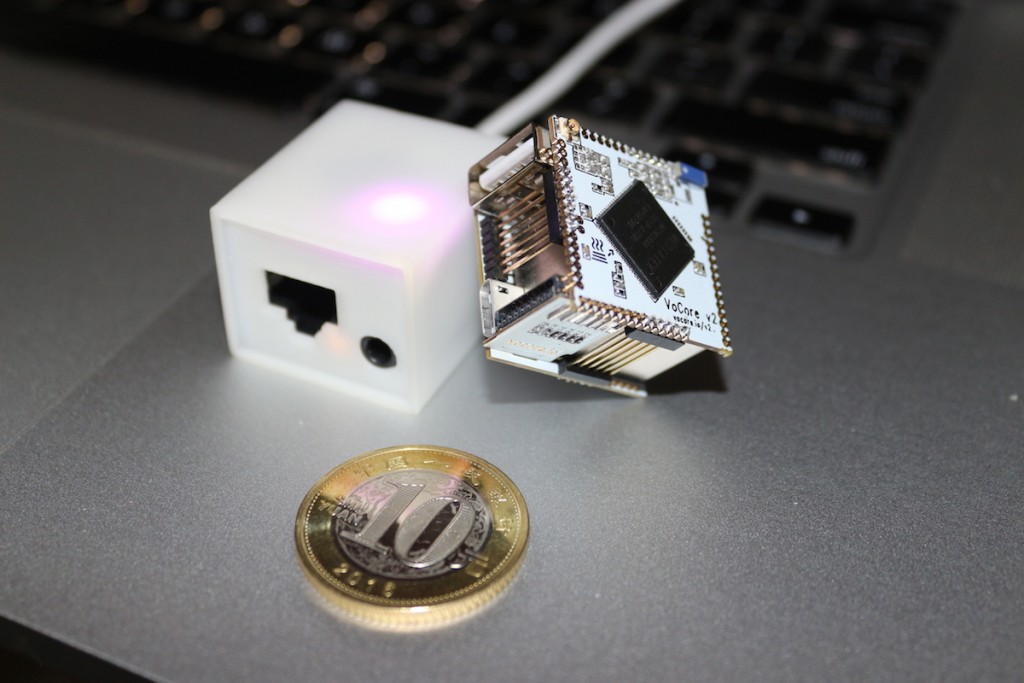

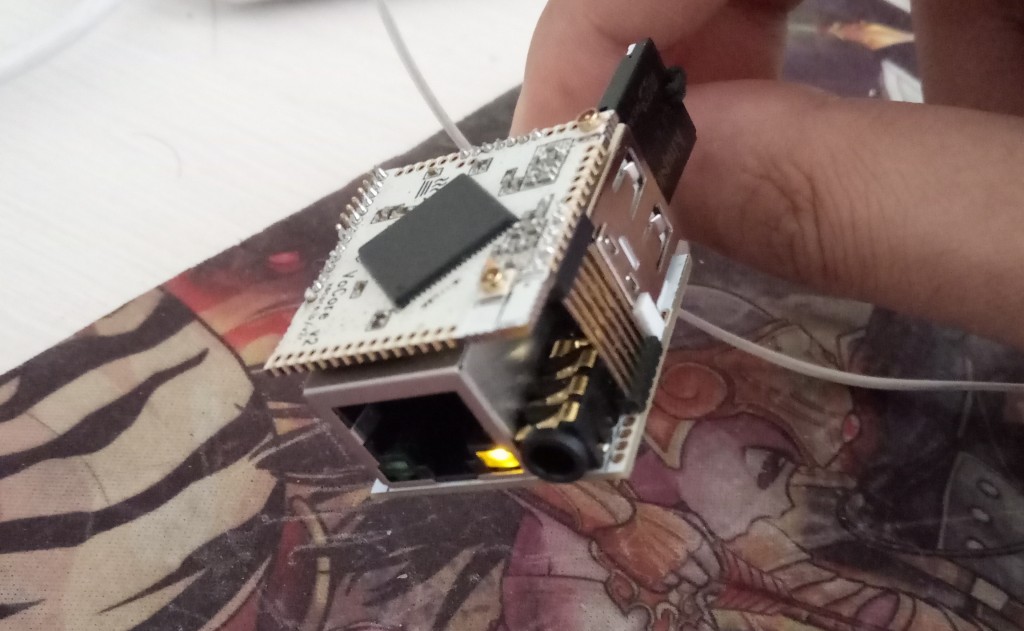

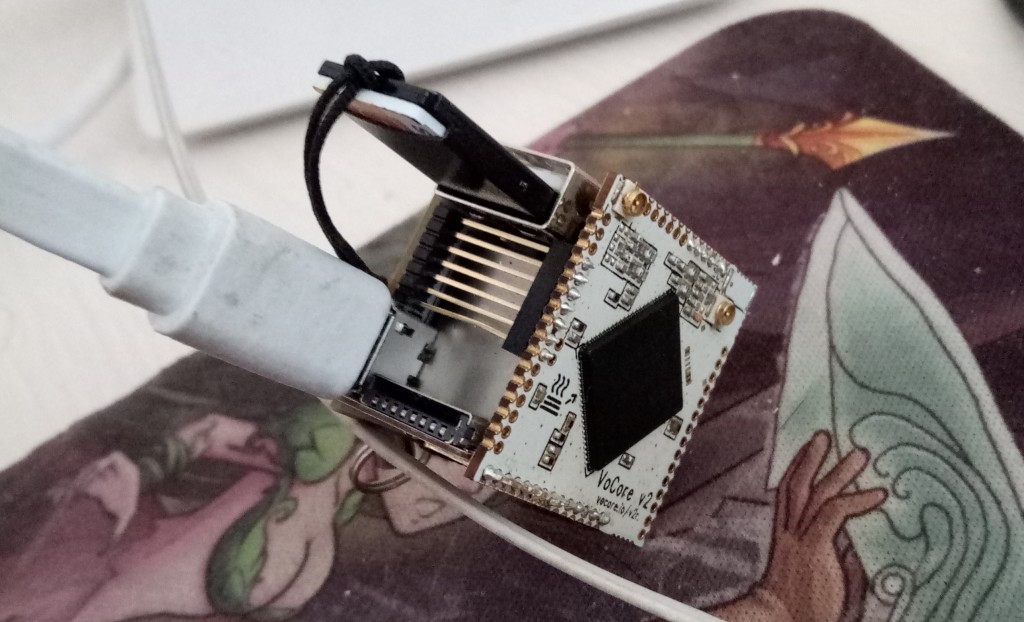

VoCore2 is almost ready, production process is smooth for now, I am thinking if it is possible to use exists technology and production process make something even cheaper. After a lot of test, it comes, VoCore2 Lite!

PS: We have limited production capacity, but I promise one people have one piece at least.

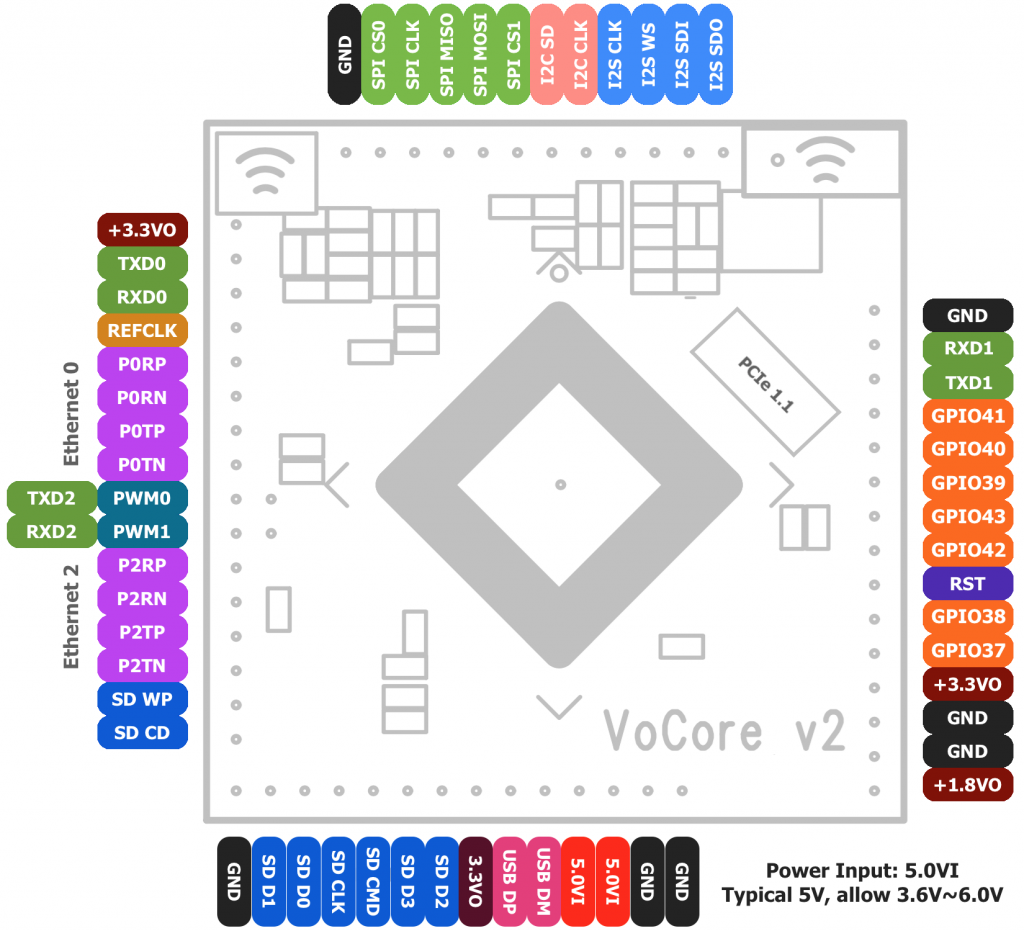

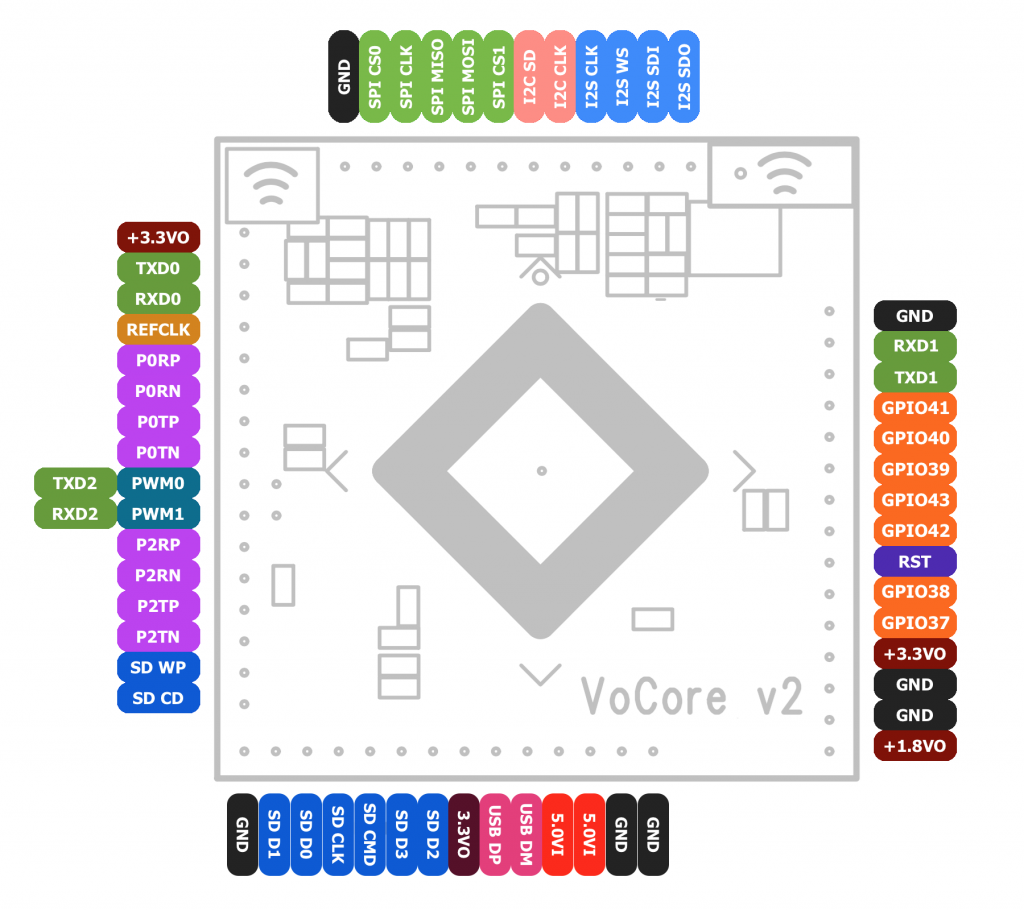

Compare VoCore, VoCore2 and VoCore2 Lite:

|

VoCore |

VoCore2 Lite |

VoCore2 |

| Price |

19.99USD |

3.99USD |

11.99USD |

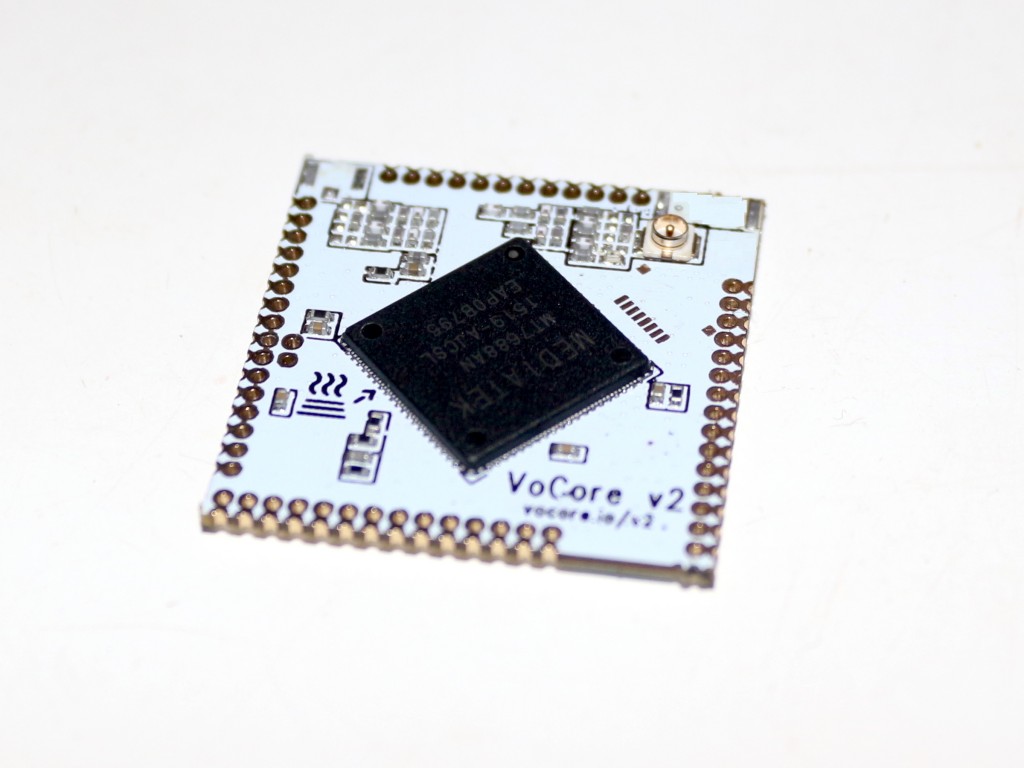

| CPU |

RT5350, 360MHz |

MT7688AN, 580MHz |

MT7628AN, 580MHz |

| Memory |

32MB SDRAM |

64MB DDR2 |

128MB DDR2 |

| Storage |

16MB NOR |

8MB NOR |

16MB NOR |

| Antenna Slot |

x1 |

x1 |

x2 |

| On-Board ANTENNA |

√ |

× |

√ |

| Wireless Speed |

~75Mbps |

~150Mbps |

~300Mbps |

| Ethernet Port |

x5 |

x1 / x5* |

x1 / x5* |

| Ethernet Speed |

100Mbps |

100Mbps |

100Mbps |

| SPI Master |

√ |

√ |

√ |

| SPI Slave |

√ |

√ |

√ |

| SPI DMA |

× |

√ |

√ |

| USB 2.0 Host |

√ |

√ |

√ |

| USB 2.0 OTG |

√ |

× |

× |

| PCIe 1.1 |

× |

× |

√ |

| SD Support |

SPI |

√ |

√ |

| GPIO |

> 30** |

>=40** |

>= 40** |

| UART |

x2 |

x3 |

x3 |

| PWM |

– |

x2 |

x2 |

| Power Consumption |

138mA |

74mA |

74mA) |

People may ask, is that price lower than the cost? The answer is it is not, but it is very very very close to the cost, and only for us with the experience of production VoCore2(we reuse the VoCore2 tech, test jig, test app, to save cost etc…). Just hope students and other cost sensitive people will have a chance to play with the most advanced IoT board. Feel happy just like the first time I made VoCore.

Final, please help us spread the news! Good luck!